搜索结果: 1-15 共查到“工学 TSV”相关记录15条 . 查询时间(0.046 秒)

中国科学院微电子所在高密度低应力硅通孔(TSV)研究方面取得新进展(图)

高性能 集成 器件

2024/6/28

2024年6月26日,微电子所新技术开发部微系统技术实验室焦斌斌研究员团队在高密度低应力硅通孔(TSV)研究方面取得新进展。三维(3D)集成技术是制造低功耗、高性能和高集成密度器件的必备技术,有望突破摩尔定律限制。TSV作为3D集成的核心技术,具有缩短互连路径和减小封装尺寸的优势。目前,高密度TSV互连在近传感器和传感器内计算、混合存储器立方体、高带宽存储器(HBM)、互补金属氧化物半导体(CMO...

TSV工艺X射线像素阵列探测器研究取得重要进展(图)

TSV工艺 X射线 像素阵列 探测器

2020/12/24

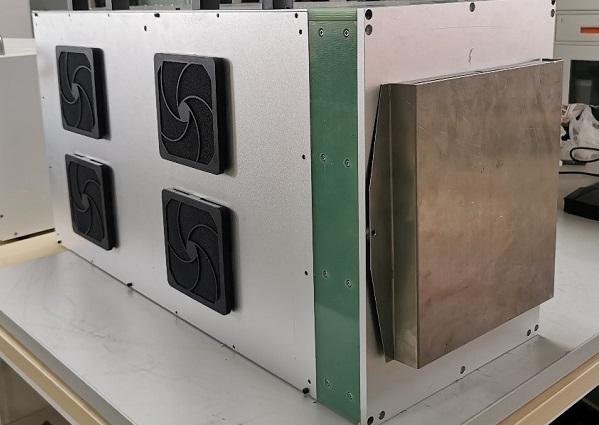

近日,中科院高能所同步辐射硅像素探测器研发团队在新型像素阵列探测器研究方面取得重要进展,团队成功研制出基于硅通孔技术(Through Silicon Via,TSV)的探测器工程样机。TSV技术的成功应用大幅缩小了模块间的缝隙宽度,同时还改善了探测器在低能区的响应。这一进展标志着高能所在先进X射线像素探测器的设计、工艺研究及系统集成上达到了国内领先水平,所有关键技术及工艺方法全部实现国产化,样机性...

基于TSV绑定的三维芯片测试优化策略

SoC 测试 3D SoC 测试优化 测试成本

2017/1/4

本文提出一种三维片上系统(3D SoC)的测试策略,针对硅通孔(TSV,Through Silicon Vias)互连技术的3D SoC绑定中和绑定后的测试进行优化,由于测试时间和用于测试的TSV数目都会对最终的测试成本产生很大的影响,本文的优化策略在有效降低测试时间的同时,还可以控制测试用的TSV数目,从而降低了测试成本.实验结果表明,本文的测试优化策略与同类仅考虑降低测试时间的策略相比,可以进...

TSV转接板组装工艺过程引起的封装结构翘曲和应力对微凸点可靠性有重要影响。该文采用有限元方法,分析了TSV转接板封装自上至下和自下至上两种组装工艺流程,通过比较工艺应力/应变和翘曲得到较优工艺流程;针对优选工艺流程,分析了不同工艺步微凸点的力学行为,重点关注封装结构中微凸点定位对微凸点可靠性的影响。结果表明:自上至下组装工艺流程较优;微凸点位置设计应尽量避开下填料边缘,当微凸点正好位于TSV上方时...

硅通孔(TSV)技术作为实现三维(3D)封装的关键而被广泛关注。该文研究了在温度载荷作用下TSV转接板上铜和硅的应力状态,给出了通孔为完全填充铜和部分填充铜两种情况下的应力解析解,并讨论了孔距对转接板应力的影响。建立了TSV转接板的二维有限元模型,并用于验证解析解的适用性。结果表明:当TSV孔距达到孔直径的3倍以上时,解析解可以给出准确的转接板上铜和硅的应力结果;通过减薄镀铜层可以减小硅上的应力;...

来自瑞典歌德堡的查默斯理工大学的研究人员发现,以碳纳米管来填充采用硅穿孔技术(TSV)连结的3D芯片堆栈,效果会比铜来得更好。TSV是将芯片以3D堆栈方式形成一个系统,而非将它们平行排列在电路板上,以提高芯片之间通讯的速度;但遗憾的是,目前用以填充硅晶孔洞的铜,却会导致热膨胀的问题,因为铜遇热会比周围的硅材料膨胀更多。

微电子所发起的首个硅通孔(TSV)技术攻关联合体在京成立(图)

微电子所 硅通孔 成立

2011/10/28

2011年7月9日,在国家02专项和中国封装测试联盟的支持下,由中国科学院微电子研究所发起的国内首个硅通孔(TSV)技术攻关联合体在北京宣告成立并启动了第1期攻关项目。科技部02专项责任专家于燮康,02专项专家组组长、中国科学院微电子所所长叶甜春以及近30家企业和科研单位代表参加了启动会。

2011年7月9日,在国家02专项和中国封装测试联盟的支持下,由中国科学院微电子研究所发起的国内首个硅通孔(TSV)技术攻关联合体在北京宣告成立并启动了第1期攻关项目。科技部02专项责任专家于燮康,02专项专家组组长、中科院微电子所所长叶甜春以及近30家企业和科研单位代表参加了启动会。

美国战区支援舰(TSV)(图)

美国 战区 支援舰(TSV)

2011/11/17

美国战区支援舰(TSV) "战区支援舰"(TSV)是美国陆军正在努力发展的一种舰船。美军对它的要求是能够横穿大洋和战区、持续航速达40节(1节=1.8公里/小时)左右,主要用于在战区内提供补给、运送陆军预置物资及人员,可充分发挥速度和灵活性上的优势,是完成美陆军未来"战区内运输任务"的重要装备。

Novellus开发全新TSV封装铜底层技术

开发 TSV封装 技术

2011/10/31

诺发系统(Novellus)日前宣布开发出一套全新先进的铜阻障底层物理气相沉积(PVD)制程,其将用于新兴的贯穿硅晶圆通路(TSV)封装市场,该制程使用诺发INOVA平台,并搭配特有的中空阴极电磁管(HCM)技术制造出高贴附性的铜底层。

杜邦推出PerMX 3000感光型干膜介电材料 用于TSV、WLP及MEMS(图)

感光型干膜 TSV WLP MEMS

2011/11/1

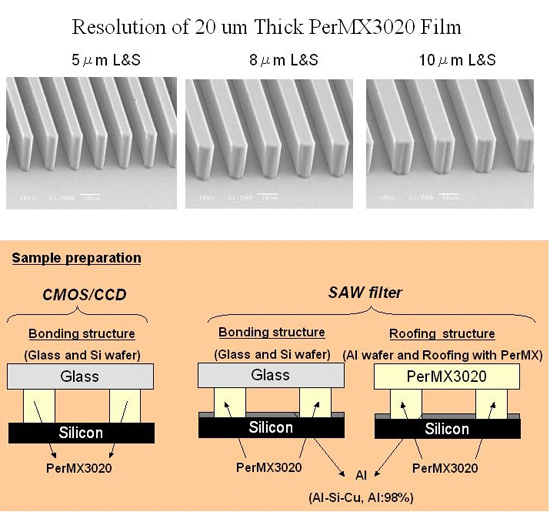

杜邦电子科技事业部旗下晶圆级封装解决方案(Wafer Lavel Packaging Solutions)推出DuPont PerMX 3000感光型介电干膜光阻( PerMX 3000 photodielectric)。这是杜邦首度推出的新一系列永久性高解析能力并具有低温制程能力的环氧树脂光阻,特别适合用于3D及直通硅晶穿孔(3D/TSV)、晶圆级封装(WLP)以及微机电(MEMS)的用途上。这...

日本早稻田大学开发出低成本3D TSV布线工艺

开发 成本 TSV布线工艺

2011/11/3

据日经BP社报道,日本早稻田大学发布了能够利用硅通孔(TSV)布线以低成本制造三维积层LSI的工艺。该工艺由早大大学院先进理工学研究科庄子研究室开发,日本IBM东京基础研究所也予以参与。

亚微纳公司首次推出TSV工艺整合设备Versalis fxP(图)

工艺整合 解决方案

2011/11/3

亚微纳技术公司(AVIZA Technology),一家服务于全球半导体业及相关市场的先进半导体主要生产设备及工艺技术供应商在日前宣布推出Versalis fxP系统。它是一个200/300mm集群系统,专为利用穿透硅通孔技术制造三维集成电路而设计。亚微纳公司在开发此类独一无二的研发用工艺整合解决方案方面处于领先地位,该技术可包含数个不同工序,包括蚀刻、PVD及CVD,其目的是为了提供快速制造出功...