搜索结果: 1-15 共查到“电子科学与技术 VLSI”相关记录34条 . 查询时间(0.046 秒)

东南大学单伟伟、杨军团队在2019 Symposia VLSI Technology and Circuits国际会议发表高能效AES电路成果(图)

东南大学 单伟伟 杨军 2019 高能效 AES电路

2019/8/8

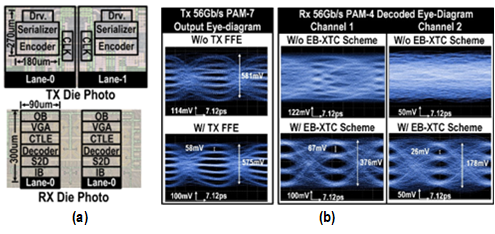

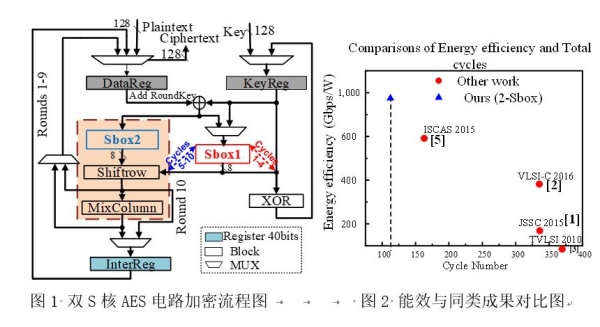

2019年6月9至14日,电子科学与工程学院单伟伟教授、杨军教授等赴日本参加Symposia VLSI Technology and Circuits会议。单伟伟教授在Symposium on VLSI Circuits分会的C20 session作报告,主题为“A 923Gbps/W, 113-Cycle, 2-Sbox Energy-efficient AES Accelerator in 2...

中国科学院微电子研究所在2019 VLSI国际研讨会上展示最新研究进展(图)

2019 VLSI 国际研讨会 研究进展

2019/6/25

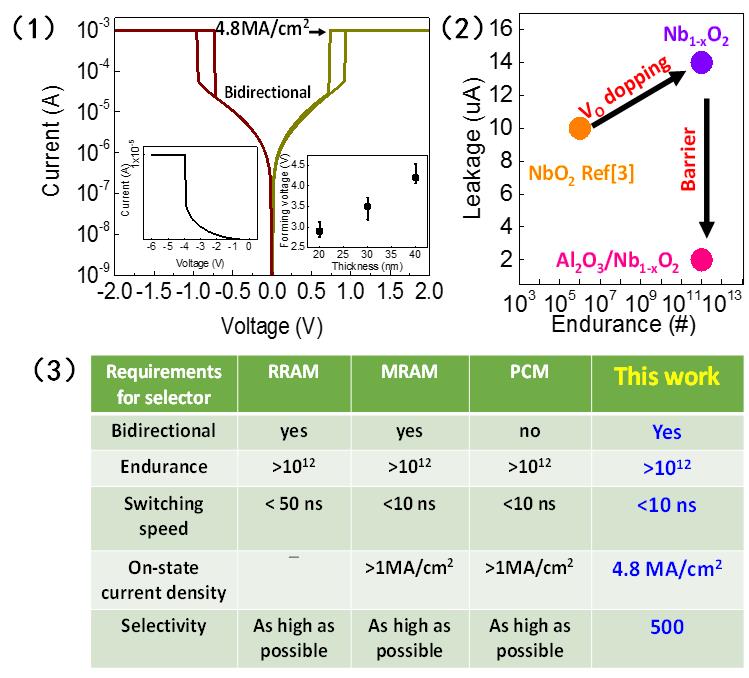

近日,2019 Symposia on VLSI Technology and Circuits(简称VLSI国际研讨会)在日本召开。微电子所刘明院士科研团队在会上展示了高性能选通管的最新研究进展。

山东大学陈杰智教授课题组电报噪声随机数发生器研究成果在2018 Symposium on VLSI Technology大会发表(图)

山东大学 陈杰智 教授 课题组 电报噪声 随机数发生器 2018 Symposium on VLSI Technology

2018/6/25

2018年6月18日至6月22日,超大规模集成电路和半导体器件领域的顶级会议"2018 Symposium on VLSI Technology"在美国夏威夷举行。山东大学信息科学与工程学院陈杰智教授课题组与英国利物浦约翰摩尔斯大学纪志罡教授课题组共同发布了基于器件随机电报噪声(RTN)的超低功耗真随机数发生器的最新研究成果。陈杰智教授团队在纳米器件电报噪声领域深耕多年,其研究涵盖了噪声物理机理及...

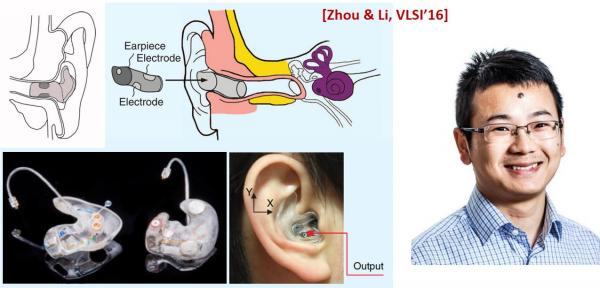

近日,电子科技大学在医疗集成电路研究领域取得重大进展。电子科技大学微电子与固体电子学院集成系统实验室博士生周雄的论文“A wearable ear-EEG recording system based on dry-contact active electrodes”(基于有源干电极技术的可穿戴外耳道脑电采集系统)成功入选2016年第30届超大规模集成电路会议(Symposium on VLSI ...

Configuration of VLSI Arrays in the Presence of Defects

Circuit area fault tolerance percolation theory probabilistic analysis queuing processes systolic arrays

2015/8/14

The penalties for configuring VLSI arrays for yield enhancement are assessed. Each dement of the fabricated array is assumed to be defective with independent probability p. A fixed fractmn R of the el...

Configuration of VLSI Arrays in the Presence of Defects

Circuit area fault tolerance percolation theory probabilistic analysis queuing processes systolic arrays wafer-scale integration wire length

2015/8/12

The penalties for configuring VLSI arrays for yield enhancement are assessed. Each dement of the fabricated array is assumed to be defective with independent probability p. A fixed fractmn R of the el...

On Detection, Analysis and Characterization of Transient and Parametric Failures in Nano-scale CMOS VLSI

Automatic Test Pattern Generation Crosstalk Design-for-Testability Integrated Circuit Intermittent Failure Soft Error

2014/11/7

As we move deep into nanometer regime of CMOS VLSI (45nm node and below), the device noise margin gets sharply eroded because of continuous lowering of device threshold voltage together with ever incr...

一类易于VLSI实现的对称双正交小波设计方法研究

对称双正交小波 格形结构 双正交滤波器组 线性相位

2010/4/12

该文提出了一类对称双正交小波的设计方法。该类双正交小波的小波滤波器组具有格形结构,实现该小波变换的分析滤波器组和综合滤波器组满足双正交条件和正则性条件,且设计的各滤波器均为实数二进制系数,因而该小波变换易于高速VLSI实现。文中的理论推导和设计实例,均验证了该设计方法的有效性。

VLSI-cell placement technique for Architecture of Field Programmable Gate Array (FPGA) design

Field Programmable Gate Array (FPGA) Space Vector Pulse Width Modulation (SVPWM) Configurable Logic Blocks (CLBs)

2010/1/11

The Field Programmable Gate Array (FPGA) is an on field programmable device which can be designed for different applications. Various types of software are available for its synthesis. The cell placem...